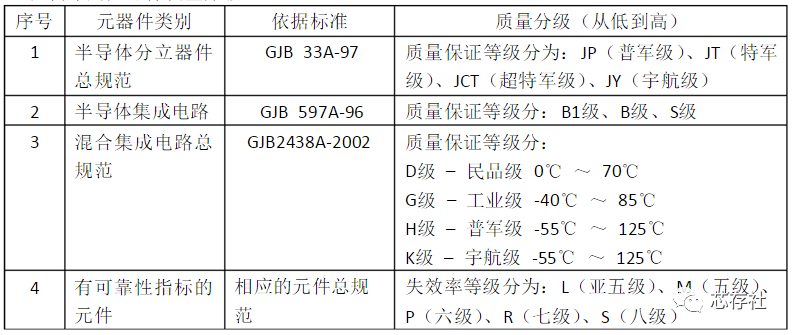

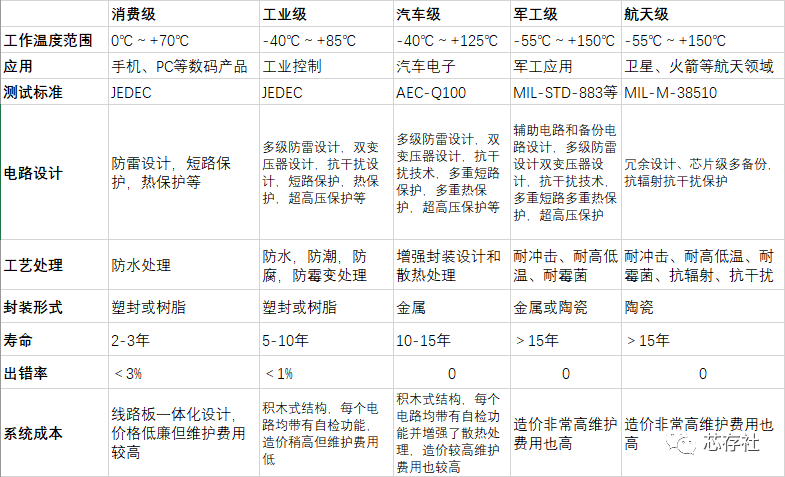

常见的芯片等级一般是按照使用温度、辐射、抗干扰等来分级。等级分为以下5类: 民用级(消费级)、工业级、汽车级(车规级)、军工级、航天级。

民用级(消费级)温度为: 0C~+70°C,市面上常见的、经常交易的那种,电脑、手机、数码产品等能看到的基本上都是消费级的,价格便宜、更新换代快、最常见最实用。

工业级温度为: -40°C~+85°C,比军工级档次稍微低一点、价格次之、精密度也稍微差些。

汽车级(车规级)温度为: -40°C~125C,主要在汽车上使用的电子元器件使用温度要求更高、稳定性要好、价格比工业级贵些

车规级顾名思义就是使用满足汽车等级的元器件,车规级的标准是AEC-Q系列标准。AEC-Q100适用于芯片,AEC-Q101适用于分立半导体器件,AEC-Q102适用于分立光电子器件,AEC-Q103适用于MEMS器件,AEC-Q104适用于多芯片模组,AEC-Q200适用于无源元件。

AEC全称汽车电子协会(Automotive Electronics Council),是1993年美国三大公司克莱斯勒、福特和通用发起建立的可靠、高质量电子元器件标准的标准化机构,旨在建立可靠、高质量电子元器件的通用标准。AEC的成员分为两种,一种是永久成员,通常为车辆公司,一种是技术成员,一般是芯片公司。AEC提供测试平台,芯片在流片后必须经过AEC-Q系列测试环节才能通过车规级验证。因此,AEC-Q测试也称为芯片前装上车的“基本门槛”。

有了测试就需要有结果,芯片经过测试后会得出该批次的整体通过率,也就是良率,良率决定了芯片最终的分级范围。依据DPPM(Defect part per million 每百万缺陷机会中的不良品数)标准,消费芯片小于500,车规为0~10个缺陷。工规介于两者之间,具体要求会随着客户需求微调。

从车规级要求来看,它的工作温度要求达到-40℃到125℃,还需要具有防雷、防潮、防震等性能。所以车规级芯片往往在封装时要考虑到散热与密封性问题。目前汽车芯片较多采用SIP封装,将大部分对计算稳定性需求大的模块集成在一起统一进行封装保护,也同时减少了不同模块之间通信的距离,减少数据传输时受到影响的可能性。

军工级温度为: -55°C~+150°C主要使用在导弹、坦克、航母等军工领域,军工里面的电子元器件,任何一个部分拿出来,都是最稳定,最可靠、抗干扰、精密度高。

航天级温度为: -55°C~+150°C航天级元器件是元器件的最高级别,主要使用在火箭、飞船、卫星等航天领域,使用温度与军工级一致,但在军工级的基础上增加抗辐射、抗干扰功能。

如何做到抗辐射?

其实封装对芯片的保护是有限的,高能粒子流可以打穿芯片的封装材料,进入芯片内部对芯片造成破坏。

抗辐射加固主要有设计和工艺两种加固技术,或者根据需要组合使用这两种技术。

从广义上讲,抗辐射加固设计包括材料设计、系统设计、结构设计、电路设计、器件设计、封装设计、软件设计等。从狭义上讲,一般是指采用电路设计和版图设计减轻电离辐射破坏的方法。

工艺加固是用特殊的工艺进行抗辐射加固的技术。工艺步骤可以是制造商或军方专有的,也可以是以加固为目的将特殊的工艺步骤加入到标准制造商的晶圆制造工艺中去。抗辐射加固工艺技术具有高度的专业化属性和很高的复杂性。

从系统、结构、电路、器件级的设计技术方面进行抗辐射加固设计可以采用以下方式进行抗辐射加固设计:

一是采用多级别冗余的方法减轻辐射破坏,这些级别分为元件级、板级、系统级和飞行器级;

二是采用冗余或加倍结构元件(如三模块冗余)的逻辑电路设计方法,即投票电路根据最少两位的投票确定输出逻辑;

三是采用电路设计和版图设计以减轻电离辐射破坏的方法。即采用隔离、补偿或校正、去耦等电路技术,以及掺杂阱和隔离槽芯片布局设计;

四是加入误差检测和校正电路,或者自修复和自重构功能;

五是采用电路设计和版图设计以减轻电离辐射破坏的方法。即采用隔离、补偿或校正、去耦等电路技术,以及掺杂阱和隔离槽芯片布局设计。

此外,使用加固模拟/混合信号IP技术和SIGE加固设计技术也是提升芯片抗辐射能力的有效途径。

抗辐射芯片加固专用工艺越来越多地与加固设计结合使用。因为抗辐射加固工艺技术具有非常高的专业化属性和高复杂性,因此只有少数几个厂家能够掌握该项技术。

例如,单粒子加固的SOI工艺和SOS工艺,总剂量加固的小几何尺寸CMOS工艺,IBM的45nm SOI工艺,Honeywell的50nm工艺,以及BAE外延CMOS工艺等。

不同等级与规格的芯片从设计到封装、测试阶段,都有着不同的要求,使用场景也有较大不同。总的来看,规格越高的芯片,芯片冗余性设计越多,封装越严密,测试过程也越复杂严格,研发难度和成本自然越高。

上一篇:手机平板常用存储型号容量对照表

下一篇:一文看懂内存芯片的发展史